|

|

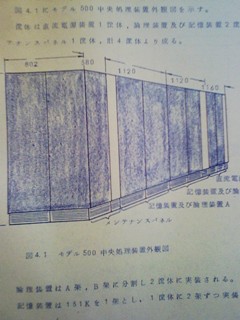

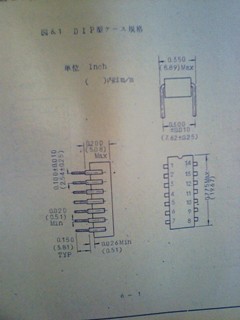

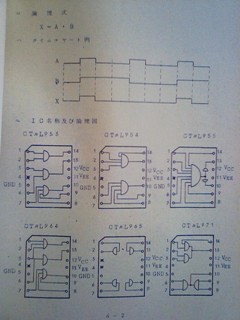

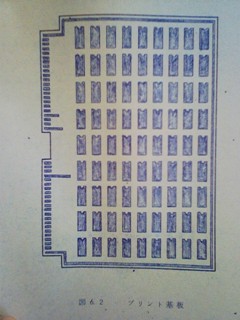

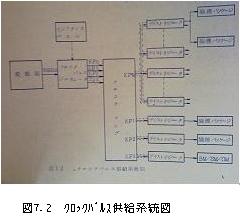

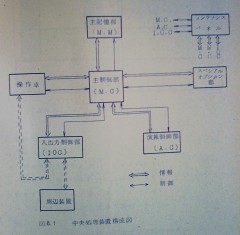

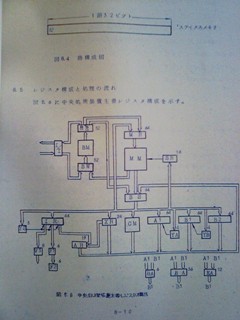

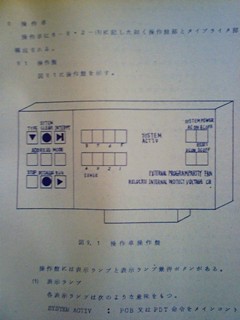

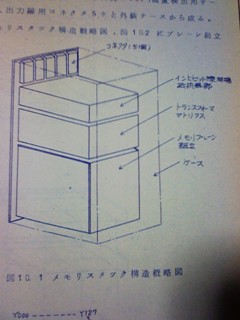

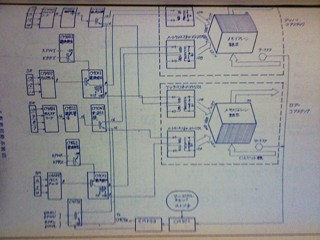

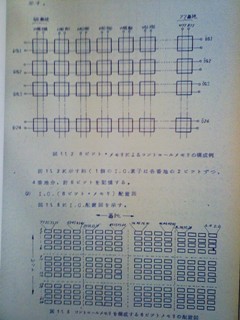

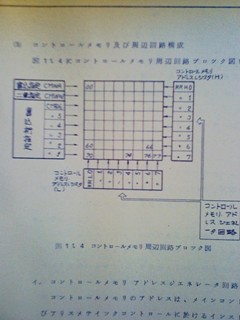

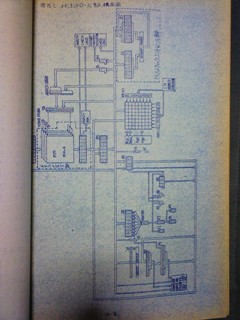

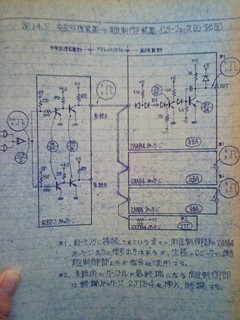

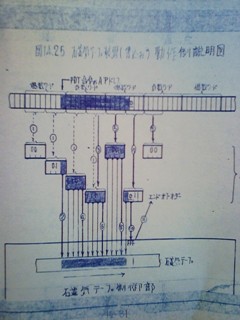

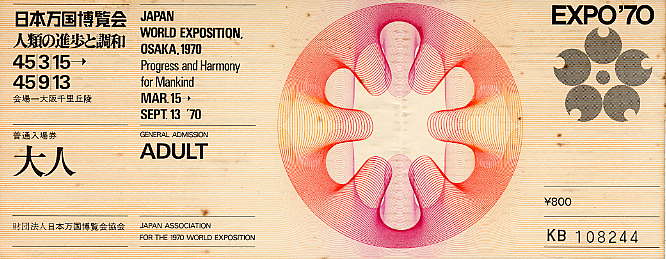

世界初のオールIC製コンピュータNEAC2200モデル500(デ処サ資料)菜翁が旨さんのほほ~ぇむ健康ペ~ジのサイトマップへHomeへ⇔随想集へ 菜翁が旨さんが初版を、千葉県習志野運輸事務所を皮切りに開始が予定されていた、運輸省の自動車登録オンラインシステム(1970年3月、自動車登録検査業務電子情報処理システム (U-SYS) 稼働開始による電算化(wikipedia))の維持管理を行うNTT(電電公社)の本社建設局及び施設局の参事官、通研(電気通信研究所:武蔵野)の研究員、三重県の鈴鹿電気通信学園教官などの管理職向けの講義録をまとめなおしたもので、初版以降は、日本電気株式会社データ処理サービス事業部のCE(ユーザ常駐技術者)向けに、MTTR短縮を目的としてCE訓練向け資料(NEC書籍登録番号:EMN-1220)として使用していたものである。 世界初!オールIC製コンピュータ,NEACシリーズ2200モデル500ハードウエア概説書 著者:菜翁が旨さん  1969年(昭和44年)10月14日初版発行 日本電気株式会社データ処理サービス事業部資料(EMN-1220)より抜粋・転載 本書は大阪大学におけるMAC(Multi Access Computer)(TSS:Time Shearing System)システム(日本のコンピュータ:阪大MAC)にみられる如く,大規模オンライン・リアルタイム・システム用として設計され,そして,中央処理装置(CPU)には国産電子計算機で初めて集積回路(IC)を全面的に採用したNEACシリーズ2200モデル500中央演算処理装置のハードウエアについてその概要説明を行っている。 本書を読むに当たっては、あらかじめ「NEACシリーズ2200モデル500説明書」(EOI-39563)を読み,理解しておくことが必要である。 目次 1. 概説 2. モデル500の特徴 2.1 オンライン・リアルタイム・システム用として具備している諸機能 (1)大容量主記憶装置 131K字から524K字まで、131K字単位で増設することが出来る。 (2)高速処理 論理素子には全てIC(集積回路)を使用している。 主記憶は1.5μsのサイクルタイムで8字同時に読み出すことにより,1字当たりのサイクルタイムを見かけ上187.5nsに短縮している。 (3)ダイナミック・リロケーション(Dynamic Relocation) 多重プログラムの実行に際しては頻繁にロールイン・ロールアウトが行われ,同一プログラムがその都度主記憶の異なった領域で実行されるのが通例であり、,これをソフトウエアのみで制御することはシステムの性能低下につながり得策ではない。 本機ではダイナミック・リロケーションをハードウエアで行うためのBRR(Base Relocation Register)を備えている。 リロケーションは4K字(4096K字)単位で行う事が出来る。 (4)記憶保護 多重プログラムの実行中は互いに独立した複数のプログラムが常にコア(主記憶)のなかに置かれており,それら相互間はプログラムの誤り等によって他のプログラムを書き換えるような誤りを犯すことは許されない。 本機ではこのような干渉を防止するために「N1118A記憶保護付加機構」及び「S0129入出力記憶保護機構」が用意されている。 記憶保護領域は4K字から4K字単位で設定することが出来る。 (5)タイマ機構 イ.課金データ作成等の用途のために中央処理装置の占有時間をメモリサイクル(1.5μs)単位で測定するために「S0128Aタイマ付加機構」が用意されている。 ロ.ハードウエア又はソフトウエアの誤りのために周辺装置と中央処理装置間のデータ移送あるいは,実行中の命令が終了しない(stall)ような事態が発生すればシステムの機能は完全に停止してしまう。 このような事態を防止するために,本機では監視タイマとして「S0128Bタイマ付加機構」が用意されている。 (6)割り込み 次に示す3レベルの割り込み機能を備えている。 イ.緊急割り込み(Urgent Intrruption) ハードウエアで発生したパリテイエラ等の異常状態の発生による割り込み。 ロ.外部割込み(External Intrruption) プログラムをより効果的に運用するための周辺制御部等からの割り込み及びマンマシン・コミュニカーションを行うための操作スイッチからの割り込み等。 ハ.内部割込み(Internal Intrruption) プログラム上の誤りにより中央処理装置の機能低下きたすような状態を検出した事による割り込み。 (7)オープン・エンドなシステム 本機に接続可能なリードライトチャンネル及び周辺制御部はそれぞれ標準8及び32に対して,16及び64とすることが出来るように「N1116Aチャンネルトランク付加機構」が用意されている。 さらにシステムアップを実現するためにはモデル500と互換機能を備えたモデル700が用意されている。 (8)割り込みの禁止・解除 プログラムの効率的な運用のため周辺制御部に対する割り込みの禁止,解除を指令することが出来る。 2.2 モデル400以下のシステムとのハードウエア構成上の比較 (1)論理素子は全てIC(集積回路)を使用している。 (2)先回り制御を行っている。すなわち、命令の先取りを行う事により命令読み出し時間を実効的にゼロにしている。 (3)大型両面パッケージを採用している。 (4)信号伝播線路での遅れ時間を少なくする筐体,架構造を採用している。 (5)主記憶のリード・ライトを8字単位として高速化している。 (6)コントロールメモリ,バッファメモリにもICを採用している。 (7)メンテナンス・パネルの採用によりMTTR(Mean Time To Repair)の短縮を計っている。 (8)メンタナンスパネルからのクロックストップ,クロックステップ機能を採用して、MTTR(Mean Time To Repair)の短縮を計っている。 MTTRの短縮もさることながら、MTBF(Mean Time Between Failure)を長くすることは、オンライン・リアルタイム・システム用コンピュータとしては最も重視されるべき性能である。 NEACシリーズ2200モデル500は、当時の技術の粋を集めた世界で最先端のコンピュータであった。 3. 諸元 3.1 構造(抜粋) 重量 200Kg (記憶装置及び論理装置A,B夫々) 消費電力 4.2KVA (記憶装置及び論理装置A,B合計) 3.2 性能(抜粋) (1)中央処理装置(CPU:Central Processing Unit) イ.方式一般 演算方式:10進、固定/浮動小数点方式 語長:可変長393K字 固定長 固定小数点=36ビット 浮動小数点 指数部=12ビット 仮数部=36ビット 命令語形式 可変長 2アドレス方式 ・1字当たり 6データ・ビット+2句読点(Pancutuation)ビット ・8字64ビット並列処理 固定長 1アドレス方式、レジスタ/レジスタ方式 ロ.回路方式 ・同期式スタテイック回路 ・クロック 単相 5.33MHz ハ.回路素子 ・IC:CTL型 ・デユアルインライン(1素子当たり14端子) ・1論理段当たり遅れ時間:7~22ns ・使用IC総数:約15,000個 ニ.演算速度 ・固定小数点加減算…6μs/5字 ・浮動小数点加減算…4.5μs/48ビット ・浮動小数点乗算…49μs/48ビット ・浮動小数点除算…18μs/48ビット ホ.一時記憶装置 ・素子…IC(1素子当たり8ビット) ・記憶容量 コントロール・メモリ・・・24ビット×54個 アキュムレータ………48ビット×5個 バッファ・メモリ……32ビット×64個 ・サイクル・タイム…187.5ns ヘ.入出力関係 ・チャンネル数 標準8 最大16 ・チャンネル速度 標準 167K字/秒(1字/6μs) 最高 500K字/秒(1字/2μs) 最低 83K字/秒(1字/12μs) ・接続可能入出力制御部 標準32 最大64 (2)主記憶装置(MM:Main Memory) イ. 記憶容量 最小131,072字 最大524,288字 ロ. 語構成 1語8字(72ビット) ハ. サイクルタイム 1.56μs/8字 ニ. アクセスタイム 0.7μs/8字 ホ. 番地選択方式 2 1/2D方式 ヘ. 使用磁心 30ミル(0.76mm外形) 4. 構造 4.1 外観  図4.1 NEAC2200モデル500外観図 論理装置はA架とB架に分割して2筐体に実装される。 記憶装置は131Kを1架として1筐体に2架ずつ実装することが出来る。 直流電源装置は右端の1筐体を占有する。 メンテナンス・パネルは中央処理装置横面に取り付けられる。 4.2 架構成 4.3 架内構造 5. 直流電源 直流電源の種類と各用途は次の通りである。 +56V…メインメモリのリード・ライトおよびインヒビット駆動用電源 -28V…メインメモリの各種駆動用電源及び周辺装置用電源 +15V…中央処理装置,メインメモリ,周辺制御部のトランジスタのVcc -15V…同上 +5.0V…中央処理装置,周辺制御部のトランジスタ回路用電源及び周辺制御部のロジカル"1"クランプ用電源 +4.5V…中央処理装置,メインメモリのIC回路のVcc +2.5V…中央処理装置,メインメモリのIC回路のロジカル"1"クランプ用電源 -2.0V…中央処理装置,メインメモリのIC回路のVcc 5.1 概要 5.2 入力AC-DC変換回路 5.3 共振型SCRチョッパ回路 6. 基本論理素子 モデル500では高速性とノイズマージンの点で優れているCTL(Complementaly Transistor Logic)型ICを使用している。 平均信号伝播速度(静特性)はDTL:18ns,TTL:10ns,CTL:5ns 6.1 ケース  図6.1 DIP型ケースの規格 6.2 論理素子 (1)アンド・ゲート  タイムチャート,IC名称,論理図 (2)インバータ (3)バッファ 6.3 記憶素子 (1)デユアル・ラッチ (2)J-Kフリップ・フロップ (3)8ビット・メモリ 6.4 非論理素子 (1)抵抗 (2)コンデンサ 6.5 スイッチング特性による選別限界値(単位ns) ICの種類 FO=4 FO=8 FO=16(c/f FO:fan-out) CTμL952 17.0 20.0 - CTμL953,954 7.0 10.0 - CTμL956 21.0 22.0 23.0 CTμL968 - 36.0 - CTμL973 - 26.0 - MμL9030 - 35.0 - c/f FO:fan-out 6.5 ICの名称と使用比率 品名 比率 CTμL952 12.6% CTμL953 11.9% CTμL954 3.6% CTμL955 1.1% CTμL956 33.1% CTμL964 1.3% CTμL965 11.2% CTμL968 1.8% CTμL971 8.3% CTμL973 11.5% MμL9030 3.6% 6.6 プリント基板 形状 A型 寸法 150mm×227.5mm×1.6mm 端子数 44(片面)×2=88 実装可能IC数 8×7=72個 層間接続 内面スルーホールメッキ  図6.2 NEAC2200モデル500のプリント基板) 7. クロック・パルス 7.1 クロック・パルスの種類と位相関係 ロジックの同期制御を行うクロックパルスは周期187.5ns、幅42nsのパルスでKP0と称する。 KP0は全てのロンリパッケージのフリップフロップ(ヂュアルラッチ及びJ-K)に供給され、フリップフロップの同期制御を行う。 一方、中央処理装置と周辺装置の間のデータ移送周期は2nsであり、これらの制御回路では周期250ns、幅42nsのパルスKP1を使用する。 その他入出力制御部で使用するKP、コントロールメモリ及びステイタスメモリの書き込みパルスKP3がある。 これらのパルスは16MHzの発振器出力を分周して得ている。 図7.1にこれらのパルスの位相関係を示す。 (図7.1は省略) 7.2 発振器 発信器は、クラップタイプ水晶発振器で16MHzの発振出力でマルチバイブレータをトリガして出力幅を設定している。 オシレータパッケージの諸元を次に示す。 構成:クラップタイプ水晶発振器 発振周波数:16MHz±0.03MHz 出力パルス巾:3.0~4.0ns可変 出力レベル:+2.6V~-0.5V 7.3 クロックの供給 図7.2にクロックパルス供給系統図を示す。  発振器(オシレータ・パッケージ)は16MHzのマルチバイブレータの出力を次段に出力する。 クロックパルス・ジエネレータ・パッケージは16MHZを3ビットのリングカウンターによって逓降して5.33MHzの基本クロックKP0をはじめKP1,KP2及びTG3を発生させる。 尚、このパッケージはメンテナンス・パネルからの制御を受けてクロック・ストップ及びクロック・ステップを行う論理回路を含んでいる。 クロックアンプ・パッケージはファンアウトを増すための増幅を行う。 デイストリビュータ・パッケイジはA架,B架内に分散配置されており,全ての論理パッケージにクロックパルスを供給する。 クロックアンプからデイストリビュータ・パッケージへのクロックパルスは75Ωの同軸ケーブルで供給されている。 7.4 クロックの位相差 各クロック間の位相差はKP3を除きクロックパルス・ゲネレータパッケージ内で分周して発生しているので調整等を行うことは出来ない。 (クロックアンプパッケージにACKA3を使用している場合にはKP0~KP3全てのクロックパルスについて、位相差及びパルス幅の調整を行うことが出来る。) クロックアンプパッケージのワンショットマルチの調整によりKP3の位相差及びパルス幅を調整することが出来る。 コントロールメモリの書き込みマージンテストはKP3の位相差をずらして測定する。 クロックアンプパッケージ内のスイッチ又はワンショットマルチの調整(ACKA3パッケージの場合)によりKP0のパルス幅を変化させて、中央処理装置のクロックマージン測定を行う。 KP0は40枚のデイストリビュータパッケージにより約350枚の論理パッケージに供給されている。 KP0のクロックスキューは各論理パッケージ間に於いて10ns以下でなければならない。 (後述の筆者雑感2に関連記述あり) 8. 中央処理装置の構成 8.1 構成 主記憶部(Main Memory) 主制御部(Main Control) 演算制御部(Arithmetic control) 入出力制御部(I/O Control) スペシャル・オプション部 S0128Aタイマ付加機構 S0128Bタイマ付加機構 S0129入出力記憶保護機構 メンテナンス・パネル部 操作卓(System Console) で、構成されている。  図8.1 中央処理装置構成図 8.2 各部概要(その1) (1)操作卓(System Console) ・操作卓には操作盤部とタイプライタ部があり、操作者(オペレータ)がコンピュータを操作・制御する唯一の操作機能を持つ装置である。 操作盤は中央処理装置に対する制御を行う押ボタンスイッチと中央処理装置の状態を示す表示ランプを有する。 ・タイプライタ部には,コントロール・モード,ペリフェラル・モード,ロギング・モードがある。 コントロール・モードは,システムの停止中に,操作者によって中央処理装置の制御,主記憶及びコントロール・メモリとの情報交換を行う。 ペリフェラル・モードはシステムの稼働中に操作者とシステムが情報交換を行う周辺装置として稼動する。 ロギング・モードはシステムが稼働中か否かに関わらず、操作者がロギング・モードとしての指定操作を行う事によって,タイプライタとして使用できる。 (2)メンテナンス・パネル (3)主記憶部(Main Memory) ・主記憶部は大容量記憶装置としての信頼性及び性能価格比の点から外形30ミルの磁心をサイクルタイム1.5nsで使用している。 ・一方モデル500で採用したICは高速である。 従って主記憶のサイクルタイムと論理回路の速度とのミスマッチングを補償する手段として論理回路にある程度の記憶機能を持たせて,主記憶との情報交換回数を減らしてマッチングをとるひつようがる。 この手段としてモデル500では主記憶との情報交換を8字単位で行う事により1字当たりの見かけ上のサイクルタイムは187.5nsとすることが出来る。 この主記憶との情報交換単位の8字を主記憶の1語(WORD)とする。 尚,パリテイ・ビットは字単位に付加・検査し,語にはもたない。 8.3 各部概要(その2:論理構成部) (1)主制御部(Main Control) メインコントロール部は命令を準備し処理順序を制御する。 アリスメテイックコントロール部及びI/Oコントロール部がメインメモリをアクセスしないメモリサイクルは,メインコントロール部が先回り制御のために次の命令の読み出し等に使用する。 メインコントロール部は次の6種の大きな動作に対して制御機能を持つ。 イ.インストラクション・フェッチ…メインメモリから命令を読み出し,実行部門が直ちに実行処理できるように準備を行う。 ロ.先回り制御…アリスメテイックコントロール部で実行中の次の命令のインストラクション・フェッチを先回りで行う。 ハ.特殊命令の実行…演算処理を伴わず且つメインメモリのアクセスを伴わない命令の実行及びアリスメテイックコントロール部で実行した命令の後処理を行う。 ニ.記憶保護の監視…記憶保護機構が動作中は監視しそれが犯され場合,割り込みを発生してプログラムに通知する。 ホ.割り込み処理…三レベルの割り込みに対して各レベルに応じた割り込みの受付制御及び割り込みモードへの移行を行う。 ヘ.操作卓,メンテナンスパネルからの制御機能の実行。 (2)演算制御部(Arithmetic control) アリスメテイックコントロール部はメインコントロール部で準備された命令のうち,演算処理を伴う命令またはメインメモリをアクセスする命令を実行する。 アリスメテイックコントロール部における処理は大別して可変長データ処理(キャラクタハンドリング)と固定長2進演算処理(サイエンチフィック・プロセシング)の二つに分けられる。 固定長2進演算処理は科学演算命令の,可変長データ処理は科学演算命令及び入出力制御命令を除いた残りの命令の処理である。 (3)入出力制御部(I/O Control) I/Oコントロール部は入出力制御命令とブートストラップ動作の実行及び周辺制御部との情報移送の制御を行う。 情報移送は,メインメモリと周辺制御部との間で行われるが,メインメモリと周辺制御部では情報移送方式及び移送速度が異なるので,ブッファメモリ(BM)を介して行われる。 周辺制御部とバッファメモリ間は一字単位で移送が行われ,バッファメモリとメインメモリの間は1語(8字)単位で行われる。 (4)スペシャル・オプション部 スペチャル・オプション部には,S0128A及びS012Bタイマ付加機構並びにS0129入出力記憶保護機構がある。 タイマ付加機構は中央処理装置のメモリサイクルの計数を行う。 S0128A,はスチールサイクル(周辺制御部とのデータ移送のためIOコントロール部が使用したメモリサイクル)を除いたメモリサイクル毎に計数される。 これは,MAC等のシステムに於いて端末毎の中央処理装置占有時間の計数を行うためのものである。 S0128Bは,中央処理装置の全メモリサイクル毎に計数され。 これはIoストール,CPUストール等を計数するための監視タイマとしてしようするためのものである。 S0129は通信制御装置に接続されて,通信制御装置を介して接続された端末に割り当てられたエリア以外のメモリーアリア(プロテクト・エリア)に対する書き込みを禁止する機能を有している。 8.4 語の構成 メインメモリ,コントロールメモリ,バッファメモリ及びリードライトチャンネルステイタスメモリはそれぞれアクセスの単位として語を構成する。 メインメモリの語の構成は,1語=8字=72ビット(うち8ビットはパリテイ・ビト)である。 モデル500もメインメモリ容量は最大524K字である。 従ってメインメモリの番地選択には2進19ビットが必要である。 8.5 レジスタの構成と処理の流れ 図8.5に中央処理装置の主要レジスタ構成と処理の流れを示す。  図8.5 中央処理装置の主要レジスタ構成と処理の流れ 図8.5に示すようにレジスタ間の情報移送はBSを中心に行われる。 一般に,n個のレジスタ間の情報移送を直接行うならば,n×(n-1)路の伝送経路を必要とするが,BSレジスタを経由することにより2n路に減じることが出来る。 BSレジスタを経由することによる伝送遅れは1クロック時である。 尚,情報転送はBSレジスタを通じて8字並列に行われる。 (1)レジスタ,カウンタ類の名称,主要用途 レジスタ,カウンタ類の名称と主要用途は次の通りである。 IR:Instruction Load Reg. メインコントロール部で処理されるべき命令を含むメインメモリの1語を常時保持する8字64ビットのレジスタ。 YS:YS Counter IRにある命令の取り出し位置を指定(キャラクタ・ポジショニング)指定する3ビットのカウンタ。 F1:F1-Reg. メインコントロールで処理中及び実行中の命令コードを保持する6ビットのレジスタ。 F2:F2-Reg. アリスメテイック・コントロールで実行中の命令コードを保持する6ビットのレジスタ。 AR:Address Edit Reg. IRから1字(6ビット)取り出した間接アドレスを編集,組み立てるための19ビットのレジスタ。 XR:Indirect/Index Address Reg. インデックス修飾または間接アドレス修飾の際その内容を,編集のため一時保持する24ビットのレジスタ。 V3:V3 Reg. IRから取り出した直後のバリアント部を保持する1字8ビットのレジスタ。 MR:Main Memory Write Inf. Reg. メインメモリ書き込むべき情報を一時保持する8字64ビットのレジスタ。 特に指定ががない限り情報は1クロック時(187.5ns)の間だけ保持される。 SR:Main Memory Address reg. アクセススメインメモリの番地を保持する16ビットのレジスタ A1:A1-Reg. アリスメテイックコントロール部で処理されるAオペランドを含むメインメモリの1語を保存する8字64ビットのレジスタ。 YA:YA Counter A1レジスタにある処理されるべき文字の位置を指定(キャラクタ・ポジショニング)する4ビットのカウンタ。 B1:B1-Reg. アリスメテイックコントロール部で処理されるBオペランドを含むメインメモリの1語または処理結果をを保存する8字64ビットのレジスタ。 YB:YB Counter B1レジスタにある処理されるべき文字の位置を指定(キャラクタ・ポジショニング)する4ビットのカウンタ。 B2:B2-Reg. アリスメテイックコントロール部で処理されるB1レジスタにあるBオペランドの次の1語をメインメモリから先取りして一時保存する字64ビットのレジスタ。 DA:Decimal Adder アリスメテイックコントロール部で可変長データ処理を行う場合の1文字の加算等の演算回路。 BA:Binary Adder アリスメテイックコントロール部で固定長2進演算処理を行う時の仮数部36ビットの2進加算回路。 インデックス修飾,アイテムマーク修飾の場合の加算にも使用する。 EA:Exponent Adder アリスメテイックコントロール部で固定長2進演算処理を行う時の指数部12ビットの2進加算回路。 BR:BM Read Inf. Reg. BMから読み出した1語を一時保持する32ビットのレジスタ。 BW:BM Write Inf. Reg. BMに書き込むべき1語の情報を一時保持する32ビットのレジスタ。 (2)各記憶部の読み出し,書き込み情報の流れ イ.メインメモリの読み出し,書き込み情報の流れ (イ)メインコントロール部及びアリスメテイックコントロール部で必要とする情報 MM――→BS――→各レジスタ (ロ)I/Oコントロール部で必要とする情報 MM――→BW――→BM (ハ)メインコントロール部での処理結果のメインメモリへの書き込み BI――→BS――→MR――→MM (ニ)I/Oコントロール部からの入力データのメインメモリへの書き込み BM――→BR――→MM 又は BM――→BR――→MR――→MM ロ.コントロール・メモリの読み出し,書き込み情報の流れ (略) ハ.バッファ・メモリの読み出し,書き込み情報の流れ (略) (3)命令実行過程に於ける情報の流れ (略) 9. 操作卓 図9.1に操作卓操作盤を示す。  図9.1 NEAC2200モデル500の操作卓操作盤 操作盤には表示ランプと表示ランプ兼押しボタンがある。 9.1 操作盤 (1)表示ランプ 表示ランプは次のような意味を持つ。 SYSTEM ACTIVE : PCB又はPDT命令をメインコントロール部又はI/Oコントロール部で実行中に点灯する。 FAN : 直流電源装置又は直流電源装置に接続される制御部の温度に以上が検出された時に点灯する。 CB : 直流電源装置に接続された制御部のサーキットブレーカが切断された時に点灯する。 PARITY : 中央処理装置が緊急割り込みモードのときに点灯する。 VOLTAGE : 直流電源装置に異常電圧が検出された時に点灯する。 PROGRAM : 中央処理装置が動作中に不正(ILLeGAL)命令コードを検出した時に点灯する。 EXTERNAL : 中央処理装置が外部割込みモードの時に点灯する。 INTERNAL : 中央処理装置が内部割込みモードの時に点灯する。 RELOCATE : リロケーション機能が動作中に点灯する。 (2)表示ランプ兼押しボタン AC ON : ・ランプ:システムにAC電源が供給されている時に点灯する。 ・ボタン:システムにAC電源を供給する。 AC OFF : ・ランプ:システムに制御用電源のみが供給されている時に点灯する。 ・ボタン:システムに供給されているACを切断する。DC OFF ランプが点灯時に有効。 DC ON : ・ランプ:システムに直流電源が供給されている時に有効。 ・ボタン:システムに直流電源を供給する。 DC OFF : ・ランプ(白)システムのDCが断の時点灯。 ・ランプ(赤)直流電源装置に異常電圧が検出され,DC OFFになった時点灯。 ・ボタン:システムに供給されているDCを切断する。 赤ランプ点灯時には異常電圧検出後の保持回路をリセットする。 SENCE1~8 ・ランプ:当該番号のスイッチがONの時点灯。 ・ボタン:当該番号のスイッチをON又はOFFの状態にする。 INTERRUPT ・ランプ:操作者が実行中のプログラムに対話を要求し,プログラムがその要求を受け付ける(SVI:Store Variant and Indicators命令を実行)迄点灯している。 ・ボタン:操作者が実行中のプログラムに対話を要求する時に押す。 SYSTEM CLEAR・ランプ:使用しない。 ・ボタン:STOPランプが点灯している時のみ有効で,磁気テープ制御部と中央処理装置に効果を及ぼす。 TYPE ・ランプ:中央処理装置でタイプライタに対するPDT(Peripheral Data Transfer)命令を発し,制御部でそれを受け付けて,データ移送の終了まで点灯している。 ・ボタン:操作卓がコントロール・モードでの時メインメモリの内容をタイプライタに打ち出す。 ADDRESS MODE・ランプ:論理装置の動作アドレス・モード表示,点灯する。 ・ボタン:STOPランプ点灯時のみ有効で,論理装置の実行アドレス・モードを切り替える。 RUN ・ランプ:中央処理装置が動作中に点灯する。 ・ボタン:中央処理装置を動作させる。 INITIALIZE ・ランプ:NITIALIZEボタンを押している間点灯する。 ・ボタン:1)中央処理装置が動作中と否とにかかわらず,操作盤上のランプ試験をおこなう。 2)STOPランプが点灯している時は,中央処理装置及び周辺制御部を書記状態にする。 3)中央処理装置が動作中(STOPランプが消灯中)のイニシアライズ機能は,SYSTEM CLEARボタンと同時に押した時のみ有効である。 STOP ・ランプ:中央処理装置及び周辺制御部が停止状態の時点灯。 ・ボタン:プログラムの実行を停止させる。 9.2 タイプライタ部 タイプライタ部は三種類の機能を持っている。 (1)コントロール・モード STOPランプが点灯し,キャリエッジが復帰している状態では,コントロール・モード機能が有効である。 ・Address Insertion・・・A△CC△MMMMMMM コントロールメモリの任意の番地(CC)にメインメモリの番地(MMMMMMM)を挿入する。 ・Print CM・・・P△CC△mmmmmmm 任意のコントロールメモリの番地(CC)の内容(mmmmmmm)をタイプライタ上に出力する。 ・Registor Dump…R△mmmmmmm△nnn 直前のAまたはPキー指定されたコントトールメモリの内容(mmmmmmm)とそのコントロールメモリによって指定されているメインメモリの内容(nnn)をタイプライタ上に出力する。 ・Type In…N1N2N3△N1N2N3△N1N2N3~(SPACEキー又はOctalキー) N1:パンクチュエーシヨンマーク指定 N2:データビットの上位3ビット N3: ” 下位 ” キャリッジが復帰した状態でSPACE又はオクタル・キーを押すとメインメモリへ情報を格納することが出来る。 メインメモリの番地の指定又は確認のため,通常A,P又はRキーのあとタイプインを行う。 ・Bootstrap…B△DD△MMMMMMM DD:周辺制御部のセクタ,トランク指定 M~M:データ移送開始番地 ・Single Instruct…S SC(シーケンス・カウンタ)で指定された1命令を実行する。 (2)ペリフェラル・モード タイプライタに対するPDT命令よりロギング・モードでなければ,ペリフェラル・モードとなる。 (3)ロギング・モード キャリエッジが復帰している時は,"L"キーの打鍵によりロギング・モードになる。 9.3 コントロール・モード動作ブロック図 (1)Aキー (2)Rキー (3)Bキー (4)Pキー (5)TYPE IN(Succeeded) (6)TYPE IN(Fail) 10. 主記憶装置 10.1 概要 ・X,Y駆動電流は振幅375mA,立ち上がり立下り共に160n,パルス巾300nsである。 ・インヒビット線の伝播時間は約50nsである。 ・センス線の読み出し出力は最悪パターンでdv1:50mV以上,dv0:11mV以下,書き込み雑音による回復時間は250nsである。 10.2 構造  図10-1.NEAC2200モデル500のメモリ・スタック構造概略図 10.3 記憶容量と実装方法 ・メインメモリは131Kから,131K単位で524Kまで増設する事が出来る。 10.4 スタック ・メモリスタックは1語72ビットを36ビットづつ2分割して1架にに2組のすたっくを使用する。 10.3 リード・ライト回路構成 (1)モジュール・アサイン(架の選択) ・架の選択はSR(Main Memory Address reg.)の19,18ビットにより行い,他の17~4ビットは架内の語の選択を行う。 (2)駆動パルス ・各種の駆動パルスは安定性を得るためにL,Cによるデレーラインにより発生される。 (3)X-Y駆動回路 ・SRの10~4ビットはX線選択を,17~11ビットはY線選択を行う。  図10-10.X-Y駆動回路系統図 (4)読み出し,書き込み回路 (5)読み出し,書き込み動作概略説明 10.4 パリテイと書き込み方式 (1)パリテイ・チェックの方式 (2)書き込み方式と書き込みパリテイの発生 (3)処理結果のパンクチュエーション・ビットの取り扱いによる命令の分類 ・EXM,PMT,MOS,MCW,LCA,SI,CI,SW,CW,SVI,MAT,MITの12命令は処理結果に対して,パンクチュエーション・ビットも書き込む。 ・残りの全命令は,処理結果に対してパンクチュエーション・ビットを書き込まない。 (4)書き込みパリテイの発生方法概要 ・前記12命令に対しては,論理装置で発生させた8ビットに対するパリテイビットをそのまま書き込む。 ・それ以外の命令に対しては,論理装置で発生させたデータ6ビットに対するパリテイビットと、再書き込みの為に読み出されたパンクチュエーションビット2ビットによりパリテイを再発生してその桁のパリテイビットとして書き込む。 ・1語8桁のうち,書き込み指定の行われない桁はパリテイを含めた全ビットの再書き込みを行う。 10.5 論理装置との接続 主記憶装置の4架は並列に接続し,両端の架内では終端を行う。 11. コントロール・メモリー 11.1 構成 (1)フリップ・フロップによるコントロール・メモリの構成例 (2)IC(8ビットメモリ)配置図  図11.3 コントロールメモリ構成図,配置図 (3)コントロール・メモリ及び周辺回路構成  図11.4 コントロールメモリ周辺ブロック図 (4)コントロール・メモリの読み出し・書き込み方法 *シングル・ワードの読み出し,書き込み *シングル・ワードの二重書き込み *ダブル・ワードの読み出し・書き込み 連続した奇数・偶数番地に同時に異なる内容の読み出し・書き込みを行う。 科学演算命令でアキュムレータに対する読み出し,書き込みをこの方式で行う。 12. メイン・コントロール部 12.1 概要 メイン・コントロール部は8.3(1)で述べた処理を行う。 12.2 命令の実行形態 メイン・コントロール部は命令コードの取り出し,A及びBアドレスの取り出し,バリアントの取り出し,AオペランドのA1及びB2レジスタへの準備を主として行う。 これをインストラクション・フェッチと呼ぶ。 その後の処理は、メイン・コントロール部で実行する命令,メイン・コントロール部で準備を必要とする命令,メイン・コントロール部で後処理を必要とする命令等に分けられる。 12.3 論理構成  図12.2 メインコントロール部構成図 (1)レジスタ,カウンタ類の名称 (2)論理構成各部の名称 MR,XR,AR,IR,F1,SRは8.5 (1)を参照 BS:レジスタ間の情報転送の中継を行う8字64ビットのレジスタ。 構成上メインコントロール部に属するが,アリスメチックコントロール部,I/Oコントロール部からも利用する。 特に指定しない限り情報は,1クロック(187.5ns)の間だけ保持する。 RR:アクセスするコントロール・メモリアドレスを保持するレジスタ。 BL:リロケーションを行う際の下位限界を4K単位で示す7ビットのレジスタ。 BH:記憶保護機構が動作中,オープンエリアの範囲を示す7ビットのレジスタ。 V3:IRから取り出した直後のヴァリアント部を保持する1字8ビットのレジスタ。 VR:チェイニングに使用するためのヴァリアント部を格納する6ビットのレジスタ。 JR:ヴァリントの処理,インデイケータ類の状態収集,コンソールのタイプイン情報の受付等を行う1字8ビットのレジスタ。 AF:インクリメント、デイクリメント操作を行うためのアドレスを保持するための19ビットのフリップフロップ。 NS:アドレス19ビットのうちYSを下位3ビットとして組み合わせる事のよって次にIRから取り出すべき文字のメインメモリでの番地を示す16ビットのレジスタ。 PS:エキストラクト中またはエキストラクト終了直後の命令の命令コードが入っているメインメモリの番地を示す19ビットのレジスタ。 YS:IRにある命令の取り出し位置(キャラクタポジション)を示す3イットのインクリメント・カウンタ。 YX:XRにセットされたインデックス・アドレス又は間接アドレスのキャラクタ・ポジショニングを行うインクリメント・カウンタ。 XC:XRにセットされた関節アドレスの空シフトの制御を行う2ビットのインクリメント・カウンタ。 Module Assign:SRの19.18ビットをデコードしたメモリ架指定信号。 Address Counter:アドレスのインクリメント,デイクリメントを行うカウンタ。 ±0,±1,±2,±4,±8の加減操作を行うことが出来る。 Pointer:Ysによってキャラクタポジショニングされた文字の取り出しを行うゲート回路。 12.4 インストラクション・フェッチ 一般にキャラクタマシンに於ける命令の取り出しは次の淳順序で行われる。 1.命令コードの取り出し 2.*Aアドレスの取り出し *間接アドレス処理 *インデックス・アイテムマーク修飾処理 3.*Bアドレスの取り出し *間接アドレス処理 *インデックス・アイテムマーク修飾処理 4.バリアント部の処理 5.命令の実行 モデル500では処理速度を上げるために命令取り出し過程に於いても並行処理を行っている。 即ち,IRからの命令コード,A及びBアドレス並びにバリアント部の抽出動作(これをエクストラクトという)に対してA及びBアドレスのインデックス修飾並びにAオペランドの読み出し動作とは並行して行われる。 12.5 主制御部(Main Control)に於ける準備及び後処理 13. 演算制御部(Arithmetic control) (略) 14. 入出力制御部(I/O Control) 14.1 概要 (1)セクタ構成 中央処理装置と周辺制御部との間のデータ移送を行うリードライト・チャンネルは,6μ/字の移送速度をもつものが2チャンネル,12μ/字の移送速度をもつものが2チャンネル,接続可能入出力トランクは入力が8トランク,出力が8トランクで,これが1セクタを構成する。 モデル500は基本構成として2セクタを有している。 N1116Aチャンネルトランク付加機構を付加することによりさらに2セクタを付加することが出来る。 データ移送は,リードライトチャンネルをインターロックすることにより4μ/字,3μ/字及び2μ/字の速度で行うことが出来る。 各リードライトチャンネルは16文字を収容するバッファメモリを持っており上記のデータ移送速度はバッファメモリと周辺制御部の間の速度である。 以下詳細省略 (2)データ移送方式 14.2 データ移送 (1)データ移送の概要 (2)インターフエイス信号 (3)インターフターフェエイス回路  図14.5 中央処理装置→周辺制御部インターフエイス回路 (4)デマンド 14.3 バッファ・メモリ (1)バッファ・メモリの"語"構成 (2)バッファ・メモリの容量 (3)バッファ・メモリとメイン・メモリの対応 14.4 各周辺装置データ移送の例 (1)PDT命令によるバッファメモリへのデータの準備 イ.チャンネル・インターロックB又はCが指定されていない場合 ロ.チャンネル・インターロックB又はCが指定されている場合 (2)各周辺装置のデータ移送の例(ノーマル・モード) イ.磁気テープ装置(正方向読取り) ロ.磁気テープ装置(逆方向読取りで水平パリテイ有) ハ.磁気テープ装置(書き込み)  図14.25 磁気テープ装置書き込み動作例の説明図 ニ.コンソール(入力) ホ.コンソール(出力) ヘ.カード読み取り装置(カラム・バイ・カラム方式) ト.カード読み取り装置(カラム・バイ・カラム方式のDTM) チ.カード読み取り装置(ロー・バイ・ロー方式) リ.カード読み取り装置(ロー・バイ・ロー方式のDTM) ヌ.カ高速製表印字装置 ル.カード穿孔装置(ロー・バイ・ロー方式) オ.カード穿孔装置(ロー・バイ・ロー方式のDTM) ワ.カード穿孔装置(カラム・バイ・カラム方式) カ.カード穿孔装置(カラム・バイ・カラム方式のDTM) ヨ.磁気デイスク装置(入力) タ.磁気デイスク装置(出力) (2)マルチプレクサ・モードの動作例 イ.アドレス・トランスファ・デマンド ロ.データ転送方式 ハ.データ入力動作の例 ニ.データ出力動作の例 14.5 I/Oコントロール部の構成 14.6 デマンドの処理 15. N1118科学演算付加機構(Scientific Control) 『N1118科学演算付加機構』と云うのは、『十進演算』とは異なって、NEAC2200シリーズ・モデル500で初めて採用された『浮動小数点の加減・乗除の二進演算』を実行する、固定長2進演算処理(サイエンテイフィック・プロセシング)付加機構(オプション)であったので、NEAC2200シリーズはもとより、NEACコンピューターの歴史で初めての『浮動小数点の加減・乗除の二進演算機構』であった。 以下略 東北大学に納入された。 日本電気・コンピュータ事業・石井善昭氏【日本電気が1955 年にコンピュータ事業を開始した当初から,その中心人物として同社を牽引してこられた石井善昭氏にインタビューした内容をまとめたものである.】 日本電気・コンピュータ技術本部長・宮城嘉男氏【NEAC シリーズ2200 モデル500 の開発:1964 〜65 年頃,大型計算機の性能競争の中で論理装置の半導体集積回路(IC)化への道は明らかで,トップランナーへの挑戦としてNEAC シリーズ2200モデル500 の開発に取り組んだ.IC の開発に,そしてその実装・配線の設計と製造にまだまったく未開拓だった分野を切り開いて進むことは,覚悟はしてはいたものの筆舌に尽くせない苦難の連続であった.】 筆者注1. NEAC2200モデル500は、IBM社のベストセラー・マシン「IBM1401」のエミュレータ・マシンとしてHoneywell社が開発したH200シリーズをノックダウン生産したNEAC2200シリーズの最上位機種としてNEC日本電気が技術の粋を集めて開発した世界初のオールIC製コンピュータで、1号機は東北大学に納入された。 筆者注2. 本書は,NTT(日本電信電話公社)が運輸省の自動車登録業務として,全国の運輸事務所を結ぶ日本で初めての業務用大規模オンラインシステムのハードウエア,ソフトウエアを含めた全面的な業務委託を受けて,日本電気株式会社へ発注したシステムのうち、NTTのハードウエア技術者教育を担当することになる武蔵野通研の研究員、鈴鹿学園教官、NTT本社技術局や施設局の調査役等の方々からなる教官に対する一連のハードウエア技術講習の「中央処理装置」を担当した筆者がそのテキストとしてまとめたものであり,その後もNECのハードウエア技術者教育資料として筆者達が活用したものである。 モデル500は,その後,NEAC2200モデル700やNTTのDIPS-1(Dendenkosha Information Processing System 1)へと,技術が継承されていった。 また,モデル500の浮動小数点の加減・乗除の二進演算を行う『科学演算付加機構』はNECのスーパーコンピュータへと技術が継承されていったもの想像している。 筆者雑感1.運輸省自動車登録システム(NECのコードネーム:Uプロ)で使用された自動車の登録情報を記録する磁気デイスクは米国のCDC(Control Data)社の高速磁気デスクシステム装置と呼ばれるもので、装置の冷却は水冷式で,一基で5平方メートル近くの巨大なものであった。 CDCは,世界最速のスーパーコンピュータ会社で日本では伊藤忠商事が代理店で,原子力産業会議等がCDCのスーパーコンピュータを導入していた。 ちなみに、この自動車登録システムは、習志野運輸事務所で初めて運用開始され、その後、全国各地の運輸事務所へと拡大・供用されたのである。 筆者雑感2.モデル500の技術習得の一貫として筆者が,検査部門で東北大学へ納入する一号機の完成検査を行っていた時のことである。 個々の命令検査の時に,いくつかの命令が,実行出来たり,出来なかったりする事象があった。 図面とシンクロスコープ(テクトロの2現象シンクロ)を睨みながら,布線ミスや図面のミスやパッケージのパターンミスなどを調べながら、少しずつ調査範囲を狭めて行ったが,どこにも間違いがなかった。 最後に考えられる事は,架内の論理パケージ内のフリップフロップに供給されているクロックパルスの論理パッケージ間でのスキュー差しか考えられない,と判断してアリスメテイックコントロール架の各段に配置されているクロック・デイストリビュータ・パッケージのクロックパルスのスキュー差を測定したところ1~2nsのずれがあるので,筆者の独断で,クロック・デイストリビュータ・パッケージの印刷配線を切断してワイヤー仮配線を半田付けしたところ,実行出来たり,出来なかったりする事象があった命令が安定に動作・稼動する事が確認出来た。 原因は,クロック・デイストリビュータ・パッケージ内でのクロックパルスの印刷配線が数センチ長すぎた事であった。 とりあえず、印刷されたパターンを切断してシールド線を最短距離でパッケージの印刷配線の上を横断して半田付けして、応急処置をして検査を継続した。 論理設計ミスではなかったことは、幸いであった。 しかし、DA(デザイン・オートメーション)により、パッケージ内の印刷パターン設計が自動化されていたが、パッケージ内でのクロックパルスの到達時間の部分にパターン設計プログラムの誤りがあったようだった。 クロック・デイストリビュータ・パッケージの印刷パターンが変更された事はいうまでもない。 参考:1nsは光が真空中で約3.3cm進む時間に相当する。 プリント配線板の上には最大72 個のIC が並べられるんですが,その布線設計が問題でした.プリント配線板は200 種類もあって,その布線設計を人手でやるというのは絶望的なんですね.それで配線パターンを自動発生させるプログラムを組み始めたんですが,なかなかうまくいかないんですよ.IC の位置をあちこち変えて試してみるんですけれど,線の引き残しがたくさん出てきて,その引き残しを人間が手でやるとエラーが出る.そんな具合でこれは塗炭の苦しみだったですね。談:元日本電気・コンピュータ技術本部長・宮城嘉男氏 筆者雑感3.モデル500の一号機は東北大学へ納入される事になっていたが、例に漏れず、本機も納期遅れにやきもきしていたところへ、やっとシステム検査にたどり着いたものの,どうしても一箇所,しかも致命的な箇所でエラーになって検査が終了できない事態に関係者一同が悩まされていた。 というのも、検査プログラムは作成者等によって正常であることが検証されたので、ハードウエアの設計不良か,システムの基幹部分であるモニタープログラム(複数のプログラムを同時に動作させるための管理プログラム)の不良か判別がつかずに検査部門によって何日かが浪費されていた。 これを見かねた筆者が、夜を徹して解析に当たった結果、モニタープログラムの些細な箇所のプログラム・ミスである事を解明した。 ハードウエアの不良でなかったことに,関係者は胸をなでおろし,筆者は,銘柄は忘れたが自席で眠らずに待っていた検査部門のトップから頂いた旨いウイスキーのダブルを一気に飲み干して、ソファーで深い眠りに着いた懐かしい想い出がある。 なぜならば,ハードウエアの不良でそれが若し,論理設計ミスであれば,設計変更ということでさらに納期が大幅に遅れることにもなりかねないからである。 NECとは別名Nouki Enki Company.でもある、なんてしゃれ込んでいた(笑) 参考:この頃は、コンピュータの故障に関しては、『MTBF』と『MTTR』が重視されていた。 『MTBF』とは、Mean Time Between Failureの略で、JIS Z 8115信頼性用語によれば, 「修理アイテムの相隣る故障の間の動作時間の平均値」と定義され,. 機械システムや情報システムなどにおける信頼性の評価の重要な指標の一つであり、設計技術者の設計指標の一つでもある。 例えば、NEAC2200シリーズ・モデル500では、プリント基板では、CTμL952、CTμL953、CTμL965、CTμL973などといった論理ICの種類毎にその種類毎にそれぞれのMTBFが計算されており、一枚の基板の使用されているICの種類と数から、そして、抵抗やコンデンサの非論理素子もMTBF率向上と基板の集積率向上を目的として複数の抵抗やコンデンサをそれぞれ一個のICパッケージ化して、同様にMTTRが計算されており、更にプリント配線はその総延長とスルーホールの数からそれぞれにもとずいて、その基板のMTBFが算出され、それら基板の総数からそのコンピュータのプリント基板全体のMTBFが算出されており、さらに、電源装置や配線やコネクタ等のMTBFも同様に算出されており、それらを合算してそのコンピュータシステム全体のMTBFが算出されていた。 また、『MTTR』とは、Mean Time To Repairの略で、故障から復旧までの時間、修理が終わるまでの時間であり、信頼性の評価のもう一つの重要な指標であり、CE(customer engineer)の技術レベルの指標の一つでもある。 そこで、『MTTR』短縮を目的として、NEAC2200シリーズ・モデル500には『メンテナンス・パネル』が取りつけられていた。 例えば、この『メンテナンス・パネル』には、クロック・パルスを操作スイッチによって一発づつ出せる機能もあった。 本書も、ユーザ現場で故障修理に当るCEのMTTR短縮を目指した著作物である。 筆者雑感4.ある日のこと、久しぶりに定時退社をするために、「お先に失礼します。」と声を出してドアのほうに向かったその時、大きな声で係長が『菜翁が旨』さんを呼ぶ大きな声が耳に入った。 片手に電話を持ったまま、「先方は君を指名しているので、今すぐに大阪へ行ってくれ・・・」ということであった。 係長と話をしている間に、事務の女性は、直ぐに新幹線の切符を総務部門から手に入れてくれて、当座のお金を係長から借用して、新婚の妻に電話を入れて、東京駅に向かった。 大阪に着くと、その足で、指定されていた住友銀行本店のコンピューター室に向かった。 到着後直ちに状況を聞き取って、図面を開いてシンクロスコープで、故障個所を探り始めた。 数時間後の空が白じむ頃に漸く、故障しているIC基板を見つけて、交換して、コンピューターは正常に動作することを確認して、ユーザーに引き渡すことが出来たのであった。 「NEAC2200モデル500」は、オンラインコンピューターではあったが、住友銀行では、まだ、バッチ処理で利用していたので、救われたものだった。 帰りに、報告を兼ねて大阪支店に立ち寄ったところ、「ゆっくりして帰ってくれ」といって『日本万国博覧会(大阪万博:EXPO'70)』の入場券をもらったので、せっかくなので、会場に行ってみた。月の石の展示パビリオンなどの人気のある所は数時間の入場待ち・・・というところばかりであったので、すぐに入れるパビリオンを2,3個所見て回ったが、徹夜疲れで、もったいないが、それどころではなかったので、見学は途中でやめて、土産も買わずに新大阪駅に向かって、新幹線は眠れる時間が長い”こだま”を選んで、車中でぐっすり眠って、その日は出社せずにそのまま帰宅した。 ・・・という思い出がある。  筆者雑感5.東大の後藤教授の発明によるパラメトロン計算機であったNEAC 1240 が、ルーマニアの経済科学研究所に輸出され、その保守技術の指導に行くCE希望者募集の話が、訓練課長の宮尾氏から朝礼であった。 当時、私は、前述のNEAC2200 M500 の技術訓練の仕事で手が離せない状況であったので、ルーマニア行きには手を挙げなかった。 当時は、カルム(KLM)で羽田からアンカレッジ経由でアムステルダムへ行って、そこからパリ行きに乗り換えて、パリからブカレストに入る経路であった。 更に、ブカレストから東京への通信手段は、ブカレストへ行った同僚の帰国話によれば、テレックスをロンドンの住商へ打って、そこで東京へ打ち直す、という方法だったということである。 ちなみに、(1)普通、コンピュータはTrue とFalseの2値論理であるが、パラメトロンコンピュータは三値の多値論理(Majority operation : 3入力多数決パラメトロン素子)で動作する。 つまり、入力三値のうち二値が同じほうをTrueとして動作するコンピュータである。 (2)菜翁が旨さんは当時、すでに英検2級を取得していたが、入社時にNECに提出した履歴書には記載していたが、宮尾課長はその時点では知らなかったようである。 菜翁が旨さんが英検2級を持っていることを後日知った宮尾課長は、ルーマニアに派遣するべきだった、と語っていた。 もっとも、その菜翁が旨さんは、同僚の帰国談を聞いて、自分が派遣されなくて良かった、と、思ったものである。 今でも、思い出すたびに、今の時代ならともかくも、当時の東欧諸国への海外渡航の状況では、ブカレストへは行かなくて良かったと思っている。 ①コンピュータ博物館(社団法人情報処理学会) ② コンピュータメインフレーム物語(NEC編)』著者:石黒功 ③石井善昭氏インタビュー:インタビューア(五十音順)旭寛治 鵜飼直哉 発田弘 山田昭彦 本稿は,日本電気が1955 年にコンピュータ事業を開始した当初から,そ の中心人物として同社を牽引してこられた石井善昭氏にインタビューした 内容をまとめたものである. ④宮城嘉男氏インタビュー:インタビューア(五十音順)旭寛治 永田宇征 発田弘 山田昭彦 国産初の商用トランジスタコンピュータ,国産初の全IC コンピュータを開発し,その後も最先端コンピュータ技術の開発を推進された宮城嘉男氏にお話を伺った。 ⑤日本のコンピュータパイオニア 宮城 嘉男 IPSJ(情報処理学会) コンピュータ博物館 ⑥日本のコンピュータパイオニア 金田 弘 IPSJ(情報処理学会) コンピュータ博物館 ⑦日本のコンピュータパイオニア 出川 雄二郎 IPSJ(情報処理学会) コンピュータ博物館 ⑧日本のコンピュータ メインフレーム 【日本電気】 NEACシリーズ2200モデル500 IPSJ(情報処理学会) コンピュータ博物館 ⑨入出タイプライターを用いたオンライン・ターミナルの設定とそれによるリアルタイム処理の実例 柴田久 有馬安春 高橋寛子 柿沼淑彦 電波研究所季報 Vol. 19 No. 100 January 1973 ⑩東北大学サイバーサイエンスセンター展示室便り④ NEAC シリーズ2200 大型計算機センター発足時に導入された日本電気(株)製NEAC シリーズ2200 です。 センターで使用した計算機は、このシリーズのモデル500(1969 年〜1971 年)とモデル500/700(1971 年~1976 年)でした ⑪シンクロスコープについて 参考:Wikipedia他 10の 10乗の 100乗 googolplex(グーゴルプレックス) 10の 303~600乗 centillion(センティリオン) 10の 120乗 vigintillion(ビギンティリオン) 10の 114乗 novemdecillion(ノウバンデシリオン) 10の 108乗 octodecillion(オクトデシリオン) 10の 100乗 googol(グーゴル) 10の 96乗 sexdecillion(セクスデシリオン) 10の 90乗 quindecillion(クィンデシリオン) 10の 84乗 quattuoudecillion(クワツーデシリオン) 10の 78乗 tredecillion(トレデシリオン) 10の 72乗 duodecillion(デュオデシリオン) 10の 68乗 無量大数(むりょうたいすう) 10の 64乗 不可思議(ふかしぎ) 10の 60乗 那由他(なゆた) 10の 56乗 阿僧祗(あそうぎ) 10の 52乗 恒河沙(ごうがしゃ)/こうがしゃ 10の 48乗 極(きょく)/ごく 10の 44乗 載(さい) 10の 40乗 正(せい) 10の 36乗 澗(かん) 10の 32乗 溝(こう) 10の 28乗 穣(じょう) 10の 24乗 杼(じょ)/じ/し Y(yotta:ヨタ) 10の 21乗 Z(zetta:ゼタ) 10の 20乗 垓(がい) 10の 18乗 E(exa:エクサ) 10の 16乗 京(けい) 10の 15乗 P(peta:ペタ) 10の 12乗 兆(ちょう)T(tera:テラ) 10の 9乗 G(giga:ギガ) 10の 8乗 億(おく) 10の 6乗 M(mega:メガ) 10の 4乗 万(まん) 10の 3乗 千(せん) k(kilo:キロ) 10の 2乗 百(ひゃく) h(hecto:ヘクト) 10の 1乗 十(じゅう) da(deca:デカ) 10の 0乗 一(いち) 10の -1乗 割(わり) d(deci:デシ) 10の -2乗 分(ぶ) c(centi:センチ) 10の -3乗 厘(りん) m(milli:ミリ) 10の -4乗 毛(もう) 10の -5乗 糸(し) 10の -6乗 忽(こつ) μ(micro:マイクロ) 10の -7乗 微(び) 10の -8乗 繊(せん) 10の -9乗 沙(しゃ) n(nano:ナノ) 10の -10乗 塵(じん) 10の -11乗 埃(あい) 10の -12乗 渺(びょう) p(pico:ピコ) 10の -13乗 漠(ばく) 10の -14乗 糢糊(もこ) 10の -15乗 逡巡(しゅんじゅん) f(femto:フェムト) 10の -16乗 須臾(しゅゆ) 10の -17乗 瞬息(しゅんそく) 10の -18乗 弾指(だんし) a(atto:アト) 10の -19乗 刹那(せつな) 10の -20乗 六徳(りくとく) 10の -21乗 虚空(こくう) z(zepto:ゼプト) 10の -22乗 清浄(せいじょう) 10の -24乗 y(yocto:ヨクト) |