そういえば、XilinxのISEの使い方がなんとなくわかってきたので、ちょっと試してみました。Vertex5(だれがPICのためにこんなクソ高いチップ使う? 笑)に16F84互換チップをフィッティングしてみた結果。

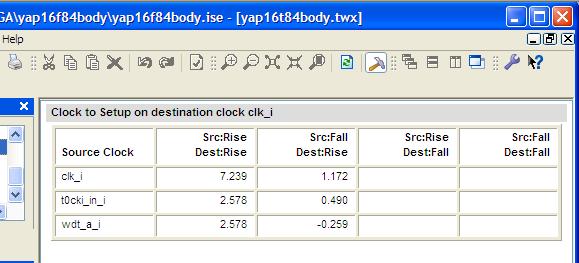

7.239nSですから、140MHz程度のクロックで動作することになります。ISEで、クリティカルパスを表示させる方法がわかりません(だれか、教えてください)。また、ISEのWarningでどうも納得いかないところがあります。夏休み明けにもう少し調べます。

では、では。

----

本日の御託

FPGAはその構造上の問題から、経験的には、2~3世代くらい前のASICと同じ位の性能しか出ません。3倍から8倍くらい遅いのです。Vertex5は65nmで製造されているそうですが、今回の回路は65nmのASICで作れば(だから、誰もつくらねえって。笑)、軽く1GHz以上のクロック(Fosc換算で4GHz)で動作するでしょう。オリジナルの16F84AはFoscは最大20MHzですから、200倍くらい速いことになります。アーキテクチャの違いを考えても、50倍程度の差はありそうです。

オリジナルはフラッシュ混載プロセスで製造していることを考慮してもかなり遅いですね。いったい、どの程度のプロセスを使っているのでしょう? 0.35μmとかでしょうか?