では、前回のA/Dコンバータを動かしてみることにします。デシメーションフィルタですが、マジにつくるのはメンドウなので、簡易的に一定期間内にHのパルスの数を数えることでいいことにしました。入力の信号は、とりあえず正弦波ですかね。Verilogはこの辺はまったく弱いので本来は自分で作らなければなりません。CORDICアルゴリズムとかでやるのでしょうが、せっかくVeritakには独自の拡張で、超越関数が使えるのでこれを使ってみることにします。

シミュレーションには、さすがに時間がかかります。我が家の最速マシン(Core2Duo E6600)でも、5分近くかかります。一般的にVerilogシミュレータはマルチCPUの恩恵を受けることができません(Veritakも例外ではありません)ので、デュアルコアのCPUでいいのは、WindowsのGUIが固まらないこと位でしょうか(笑)。

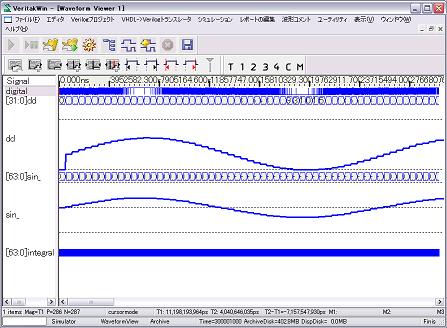

脱線しました。結果は何気にさりげにいい感じですね。信号digital_oをみると粗密波となっているのがわかります。

---

本日の御託

そりゃ、「大連立」はないだろ・・・いくらなんでも。

1 `include "analog.h"

2 `timescale 1ns/1ns

3 `define PAI (3.141592)

4 module top ;

5

6 reg clk;

7 wire `ANALOG analog ;

8 wire digital ;

9 real a, sin_ ,phase = 0;

10

11 always@ *

12 sin_ = $sin(phase) ;

13 assign analog = $realtobits( sin_ ) ;

14

15 sigma_delta_adc U_sigma_delta_adc(

16 .clk_i( clk) ,

17 .analog_i( analog) ,

18 .digital_o( digital)

19 ) ;

20

21 initial begin

22 clk = 0 ;

23 forever begin

24 # 1000 clk = ~ clk ;

25 end

26 end

27

28 integer i, c , dd ;

29

30 initial begin

31 dd = 0 ;

32 forever begin

33 c = 0 ;

34 for( i = 0 ; i <= 255 ; i = i+1 ) begin

35 @(posedge clk)

36 if( digital == 1'b1 ) begin

37 c = c + 1 ;

38 end

39 end

40 dd = c ;

41 end

42 end // initial

43

44 always@( posedge clk) begin

45 if( i == 255 ) begin

46 phase = phase + 0.0005 * 256 ;

47 end

48 end

49

50 initial begin

51 #30_000_000 $finish ;

52 end

53 endmodule