積分器をRC(抵抗とコンデンサ)タイプにして見ます。相変わらず、積分は差分式なのでむちゃくちゃ遅いです(そのうち、Veritakのルンゲ・クッタに変えます)。ついでに、ディジタル回路のなかで使いやすいように、オフセットをつけて、入力電圧の範囲を0~5Vに変更しました。

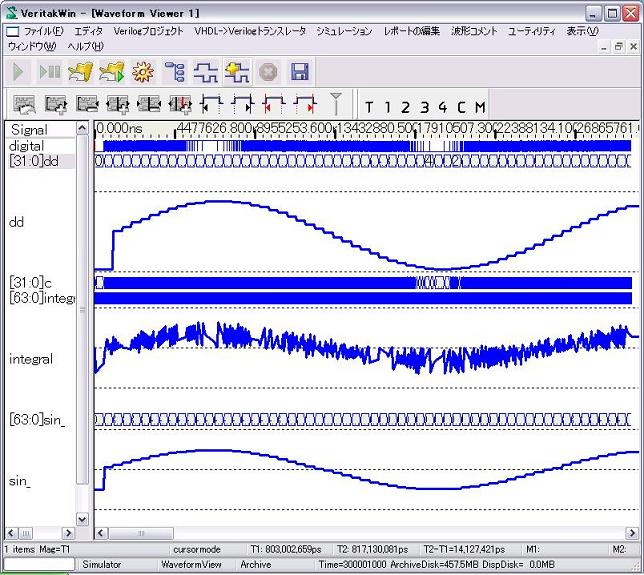

実行結果はこんな感じ。

だいたいよさそうです。この例では、前回の時定数より、1/10にしていますが特に問題はないようです。

CMOSデジタル回路では、コンパレータをどうするかは、ちょっと悩ましいですね。ディジタルICでのスレッショルド電圧を使うとすると、スレッショルド電圧に近い電圧で変化することになり、ラッチアップの可能性を考慮する必要があります。

(とりあえずこの項終わり)

---

本日の御託

横浜市水道局のホームページが更新されて、「はまピョン」のカレンダーのコーナーがなくなってしまった。orz・・・

1 // behavior model of sigma delta A/D converter

2 // with RC intergral model

3 // (c) 2007 Bakaoyaji

4 //

5 `include "ANALOG.H"

6

7 `timescale 1ns/100ps

8

9 `define RESOLUTION (1.0)

10 `define GAIN2 (0.000001)

11 `define RELATIVE_GAIN2 (`GAIN2 * `RESOLUTION)

12 `define VDD (5.0)

13

14 module sigma_delta_adc(

15 input clk_i ,

16 input `ANALOG analog_i ,

17 output reg digital_o

18 ) ;

19

20 real real_in , integ_in , integral = `VDD/2.0 ,feedback = 0.0 ;

21

22 always@ * begin // converting `ANALOG to real

23 real_in = $bitstoreal( analog_i) ;

24 end

25

26 always@ * begin // summing

27 integ_in = real_in - feedback ;

28 end // always

29

30 always begin // integral

31 # `RESOLUTION

32 integral = integral + `RELATIVE_GAIN2 * (integ_in-integral+2.5) ;

33 end

34

35 always@( posedge clk_i) begin // comparater and delay

36 if( integral >= (`VDD/2) ) begin

37 feedback <= `VDD ;

38 digital_o <= 1'b1 ;

39 end

40 else begin

41 feedback <= 0.0 ;

42 digital_o <= 1'b0 ;

43 end

44 end

45 endmodule // sigma_delta_adc